Die Size Litography

Die size lithography refers to the process of creating high-resolution patterns on a small area, typically on a semiconductor wafer, using photolithography techniques. The die size, in this context, is the physical size of the individual integrated circuit (IC) or chip that is being fabricated. The lithography process plays a crucial role in determining the final size and complexity of the die. As the demand for smaller, faster, and more powerful electronic devices continues to grow, the importance of die size lithography has increased significantly.

Introduction to Die Size Lithography

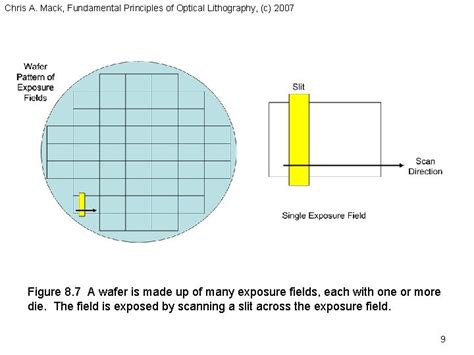

Die size lithography is a critical step in the fabrication of integrated circuits. The process involves transferring a pattern from a photomask onto a photosensitive material, called photoresist, which is coated on the wafer. The pattern is then used to create the desired structures on the wafer, such as transistors, wires, and other electronic components. The size of the die is determined by the resolution of the lithography process, which is limited by the wavelength of the light used and the numerical aperture of the lens system. As the die size decreases, the resolution requirements for the lithography process increase, making it more challenging to achieve high-quality patterns.

Lithography Techniques for Die Size Reduction

Several lithography techniques have been developed to enable the reduction of die size while maintaining high resolution and accuracy. These techniques include:

- Optical lithography: This is the most common technique used in the semiconductor industry. It uses ultraviolet (UV) light to expose the photoresist and create the desired pattern.

- Extreme ultraviolet (EUV) lithography: This technique uses a shorter wavelength of light, typically 13.5 nm, to achieve higher resolution and smaller feature sizes.

- Immersion lithography: This technique uses a liquid medium between the lens and the wafer to increase the numerical aperture and improve resolution.

- Directed self-assembly (DSA) lithography: This technique uses a self-assembling material to create patterns on the wafer, allowing for smaller feature sizes and reduced line-edge roughness.

| Lithography Technique | Resolution Limit | Wavelength |

|---|---|---|

| Optical lithography | 20-30 nm | 248-193 nm |

| EUV lithography | 5-10 nm | 13.5 nm |

| Immersion lithography | 20-30 nm | 193 nm |

| DSA lithography | 10-20 nm | None |

Challenges and Limitations of Die Size Lithography

Die size lithography is a complex process that poses several challenges and limitations. One of the main challenges is the resolution limit of the lithography technique, which determines the minimum feature size that can be achieved. As the die size decreases, the resolution requirements increase, making it more difficult to achieve high-quality patterns. Another challenge is the line-edge roughness, which can affect the performance and yield of the integrated circuit. Additionally, the cost and complexity of the lithography process can be significant, especially for advanced nodes.

Technical Specifications and Performance Analysis

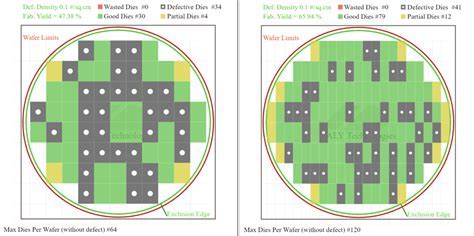

The technical specifications of die size lithography include the resolution limit, wavelength, and numerical aperture of the lens system. The performance of the lithography process is typically evaluated using metrics such as critical dimension uniformity (CDU), line-edge roughness (LER), and defect density. These metrics are critical in determining the yield and performance of the integrated circuit.

| Metric | Description | Target Value |

|---|---|---|

| CDU | Critical dimension uniformity | < 1 nm |

| LER | Line-edge roughness | < 2 nm |

| Defect density | Number of defects per unit area | < 0.1 defects/cm^2 |

What is the minimum feature size that can be achieved using EUV lithography?

+The minimum feature size that can be achieved using EUV lithography is typically around 5-10 nm, depending on the specific implementation and the quality of the photomask and photoresist.

What is the main challenge in reducing the die size of integrated circuits?

+The main challenge in reducing the die size of integrated circuits is the resolution limit of the lithography technique, which determines the minimum feature size that can be achieved. As the die size decreases, the resolution requirements increase, making it more difficult to achieve high-quality patterns.