Die Size Litography Explained

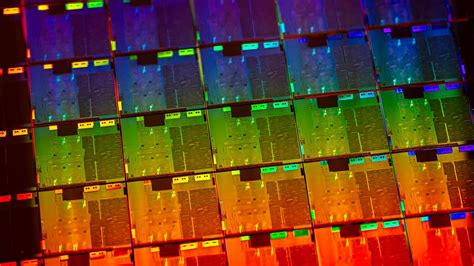

The concept of die size and lithography is crucial in the realm of semiconductor manufacturing, directly influencing the performance, power consumption, and cost of electronic devices. At the heart of this process is the die, which is the individual component or chip that contains the electronic circuitry. The size of the die, along with the lithography techniques used to create it, plays a pivotal role in determining the complexity and efficiency of the semiconductor device.

Introduction to Die Size and Lithography

In the context of semiconductor manufacturing, lithography refers to the process of creating patterns on a semiconductor material, typically silicon, to form the microscopic structures that make up the electronic circuitry of a die. The size of the die is a critical parameter as it directly affects the number of dies that can be produced from a single silicon wafer, thereby impacting production costs and efficiency. Smaller die sizes allow for more dies per wafer, reducing the cost per unit, while larger dies may offer more functionality but at a higher cost due to lower yield per wafer.

Lithography Techniques and Their Impact on Die Size

Over the years, advancements in lithography techniques have been instrumental in reducing die sizes, allowing for more complex and powerful semiconductor devices. Key lithography techniques include optical lithography, extreme ultraviolet (EUV) lithography, and immersion lithography. Optical lithography, the most traditional method, uses light to create patterns on the semiconductor material. However, as the industry has pushed towards smaller and smaller features, the limitations of optical lithography in terms of resolution have become apparent. EUV lithography, which uses a much shorter wavelength of light, has emerged as a solution for creating even smaller features, thus enabling the production of smaller and more complex dies.

| Lithography Technique | Feature Size Capability | Industry Application |

|---|---|---|

| Optical Lithography | Approx. 20-30 nm | Legacy semiconductor production |

| Immersion Lithography | Approx. 20-40 nm | Mainstream semiconductor production |

| Extreme Ultraviolet (EUV) Lithography | Approx. 5-7 nm | Advanced semiconductor production for high-performance devices |

Die Size Reduction: Challenges and Opportunities

The quest for smaller die sizes is driven by the desire for increased performance, reduced power consumption, and lower costs. However, reducing die size poses significant technological challenges, including the need for more precise lithography, improved semiconductor material quality, and innovative packaging solutions to manage heat dissipation and signal integrity. Despite these challenges, the opportunities offered by smaller dies are substantial, enabling the development of artificial intelligence (AI) chips, Internet of Things (IoT) devices, and 5G communication systems, among others.

Performance and Power Consumption

The reduction in die size through advanced lithography techniques directly impacts the performance and power consumption of semiconductor devices. Smaller transistors, which are the building blocks of electronic circuits, can switch on and off more quickly, thereby improving computational speed. Moreover, smaller transistors typically consume less power, which is critical for mobile and IoT devices where battery life is a key factor. The power consumption of a device is also influenced by the voltage scaling that can be achieved with smaller transistors, further reducing energy consumption.

For instance, the transition from a 10nm process node to a 5nm node can result in a significant increase in transistor density, leading to faster processors that consume less power. This transition not only enhances the user experience through faster execution of tasks but also contributes to the development of more energy-efficient data centers, which are critical for cloud computing and the deployment of AI applications.

What are the primary challenges in reducing die size further?

+The primary challenges include achieving the required lithography resolution, managing thermal and electrical issues at the nanoscale, and ensuring the economic viability of producing smaller dies with acceptable yields. Additionally, as transistors approach the size of a few atoms, physical limitations and variability become significant challenges.

How does die size impact the cost of semiconductor devices?

+The cost of semiconductor devices is inversely related to die size. Smaller dies allow for more devices to be produced from a single wafer, reducing the cost per unit. However, the development and implementation of technologies that enable smaller dies, such as EUV lithography, are extremely costly, which can offset some of the savings from higher yields.

In conclusion, the relationship between die size and lithography is at the forefront of advancements in semiconductor technology. As the industry continues to push the boundaries of what is possible with lithography, enabling the production of smaller, faster, and more efficient semiconductor devices, it is poised to unlock new opportunities for innovation across a wide range of applications, from consumer electronics to industrial and automotive systems. The future of semiconductor manufacturing will likely be shaped by ongoing research into even more advanced lithography techniques and the development of new materials and architectures that can overcome the challenges associated with continued die size reduction.