Linux Executable: Make Files Run With One Command

Creating a Linux executable that can run with a single command involves understanding the role of Makefiles in managing the compilation and execution of programs. A Makefile is a text file that contains a set of instructions used by the make utility to automate the building of executable programs and libraries from source code. In this article, we will delve into the process of creating and utilizing Makefiles to simplify the execution of Linux programs.

Understanding Makefiles

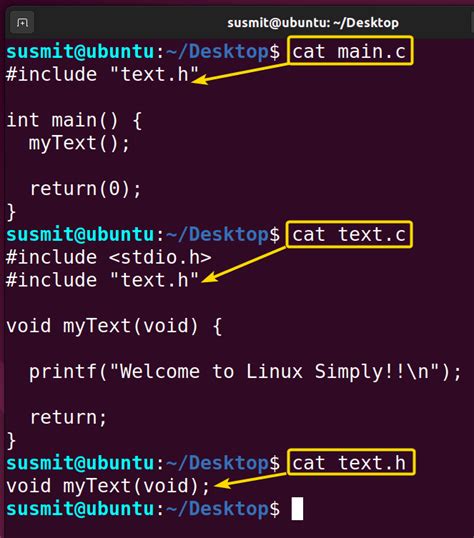

A Makefile consists of a series of rules, each of which specifies a target file and the commands required to create that target. The basic syntax of a Makefile rule includes the target, prerequisites, and commands. For instance, a simple rule to compile a C program might look like this:

target: prerequisite1 prerequisite2

command1

command2

In this context, target is the file to be created, prerequisite1 and prerequisite2 are the files required to create the target, and command1 and command2 are the actions taken to create the target from the prerequisites.

Creating a Basic Makefile

To create a Makefile for a simple C program, you would first need to define the compiler and the flags you wish to use. For example, to compile a program called hello.c using GCC with the -Wall flag to enable all warnings, your Makefile might start like this:

CC=gcc

CFLAGS=-Wall

Next, you would define the target, which in this case would be the executable file hello, and specify its prerequisite, the source file hello.c. The command to compile the source into an executable would then be specified:

hello: hello.c

$(CC) $(CFLAGS) -o hello hello.c

This rule tells make that to create the target hello, it needs the file hello.c, and the command to create hello from hello.c involves compiling hello.c with the specified compiler and flags.

| Makefile Element | Description |

|---|---|

| CC | Specifies the compiler to use. |

| CFLAGS | Defines the flags passed to the compiler. |

| Target | The file to be generated. |

| Prerequisites | Files required to generate the target. |

| Commands | Actions taken to create the target from prerequisites. |

Advanced Makefile Features

Beyond the basic syntax, Makefiles offer a range of features that can enhance the efficiency and flexibility of your build processes. These include automatic variables, pattern rules, and functions. Automatic variables, such as @</code> for the target file name and <code>^ for the prerequisites, can simplify the writing of commands. Pattern rules allow for the specification of targets and prerequisites using wildcard characters, enabling the application of a single rule to multiple files. Functions provide a way to perform complex operations, such as substituting strings or searching for files.

Utilizing Makefile Variables and Functions

To leverage the full potential of Makefiles, it’s essential to understand how to define and use variables and functions. Variables can be defined at the command line or within the Makefile itself. For example, you might define a variable SRC to hold the list of source files:

SRC = main.c utils.c

Functions, on the other hand, can be used to manipulate these variables. The $(wildcard pattern) function, for instance, can be used to find all files matching a certain pattern, which is particularly useful for automatically generating lists of source or object files.

OBJ = $(SRC:.c=.o)

This line uses a substitution reference to replace the .c extension with .o for each file in SRC, effectively generating a list of object files corresponding to the source files.

- Automatic Variables: Used within commands to refer to the target or prerequisites.

- Pattern Rules: Allow for the application of a rule to multiple targets based on a pattern.

- Functions: Enable complex operations such as string manipulation or file searching.

Best Practices for Writing Makefiles

When writing Makefiles, several best practices can help ensure that your build process is efficient, maintainable, and scalable. First, keep your Makefiles simple and focused on a single task or project. This involves avoiding overly complex rules and variables. Second, use meaningful variable names and comments to improve readability. Third, leverage the power of automatic variables and pattern rules to reduce duplication and enhance flexibility. Finally, test your Makefiles thoroughly to catch any errors or unexpected behaviors early in the development process.

Debugging Makefiles

Debugging a Makefile can be challenging due to its declarative nature and the indirect way it specifies build actions. However, several techniques can aid in the debugging process. The make -n or make –dry-run option can be used to see the commands that would be executed without actually running them. The make -d option enables debug mode, providing detailed information about the decisions make makes during the build process. Additionally, using echo statements within your Makefile rules can help trace the execution flow and variable values.

- Keep it Simple: Avoid complexity and focus on a single project or task.

- Use Meaningful Names and Comments: Improve readability and maintainability.

- Leverage Automatic Variables and Pattern Rules: Reduce duplication and enhance flexibility.

- Test Thoroughly: Catch errors and unexpected behaviors early.

What is the primary purpose of a Makefile in Linux?

+The primary purpose of a Makefile is to automate the build process of programs and libraries by specifying the commands and rules required to compile source code into executable files.

How do I create a basic Makefile for a C program?

+To create a basic Makefile for a C program, define the compiler and flags, specify the target and its prerequisites, and provide the command to compile the source into an executable. For example, for a program called hello.c, your Makefile might include rules to compile hello.c into an executable named hello.

What are some advanced features of Makefiles that can enhance build processes?

+Advanced features of Makefiles include automatic variables, pattern rules, and functions. These features allow for more complex and flexible build processes, enabling the automation of tasks such as compiling multiple source files, handling dependencies, and performing string manipulations.